在5G非连续多频段通信场景中,毫米波下变频器作为射频前端的核心模块,需同时满足双频段覆盖、高线性度、低功耗三大关键需求。近日,天津大学微电子学院马凯学教授团队在该领域取得重要突破,相关成果以“A Reusable Superheterodyne Dual-Band Down-Conversion Mixer With Hybrid Linearity-Enhanced Technique for 5G Non-Contiguous Multiband NR”为题,发表于国际顶级期刊《IEEE Journal of Solid-State Circuits》,为 5G 毫米波FR2频段通信系统提供了高性能芯片解决方案。

为解决双频段对多个本地振荡器(LO)的依赖,团队设计基于高中频(IF=6 GHz)的可复用超外差架构,通过“LO±IF”频率规划,仅需30-36 GHz单LO,即可实现24-30 GHz(LO-IF)与36-42GHz(LO+IF)双频段下变频,LO带宽需求减少50%,避免多LO带来的相位噪声与功耗问题;两个混频核心共享LO正交生成链路(QGL)与IF正交合成网络(QSN),通过Mode1/Mode2切换实现双频段独立工作,芯片面积仅1.47mm²,较传统并行架构缩小30%。

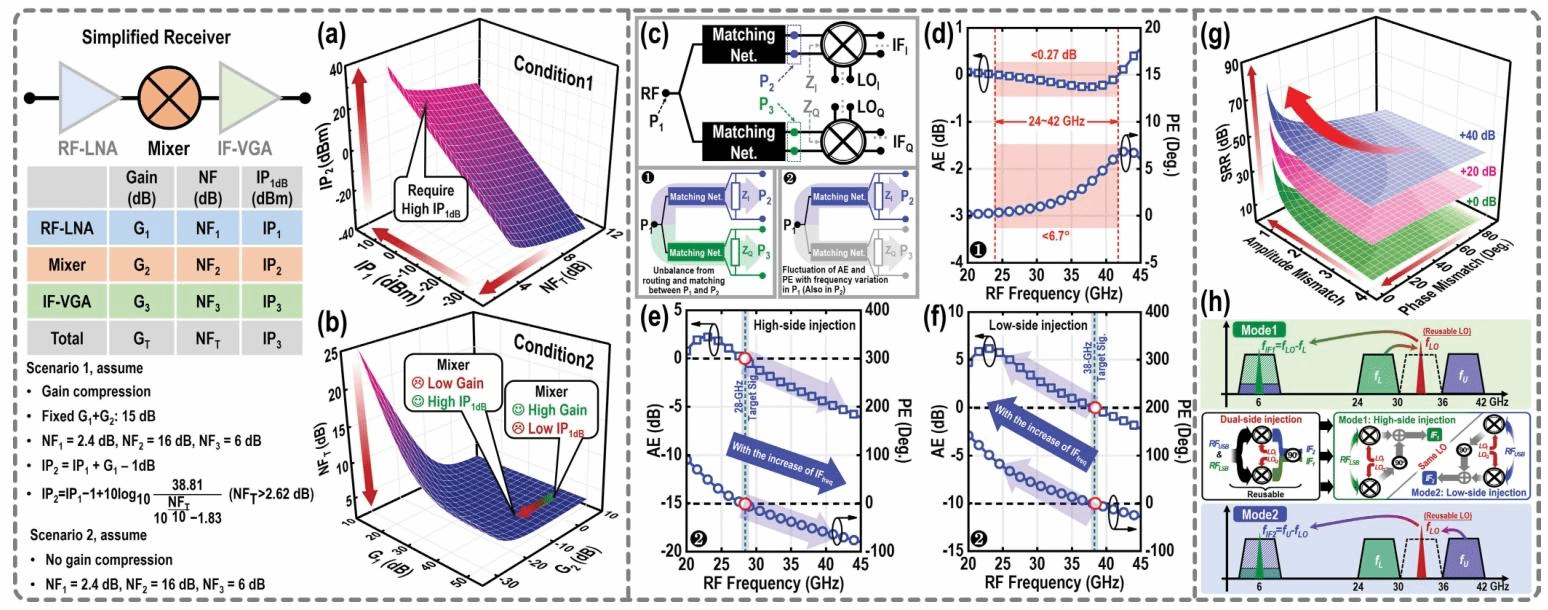

图1.基于简化通用接收机的两种场景(a)和(b);(c)基于传统哈特利架构的混频器射频通路示意图(d)P₂与 P₃之间随频率变化的仿真失配情况(e)高边注入、(f)低边注入模式下,基于特定目标频点的 P₂或 P₃引起的仿真失配情况(g)不同幅度和相位失配下的仿真边带抑制比(h)所提双频段下变频器的频率规划与设计理念

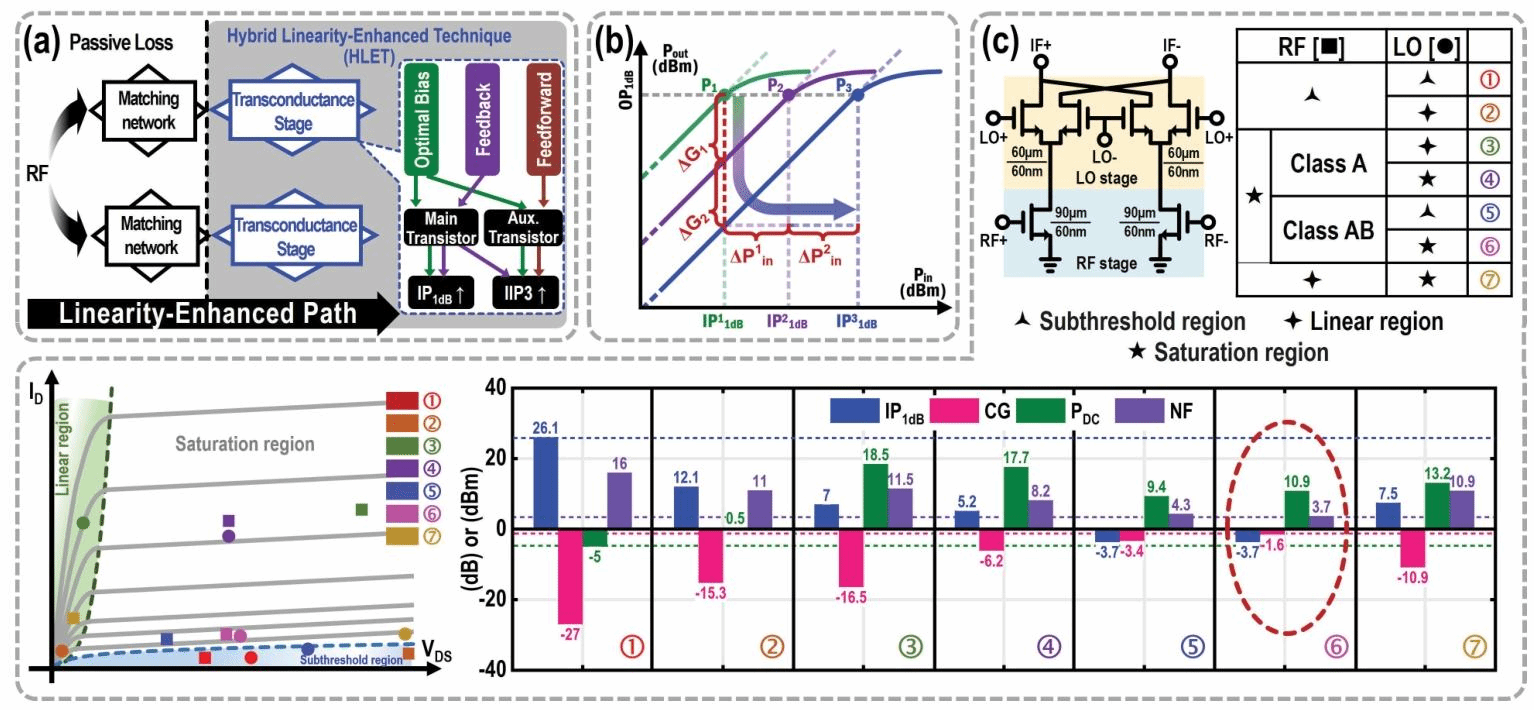

为解决线性度优化的单一性问题,团队融合“最优偏置+反馈+前馈”三重机制,提出HLET技术。将射频跨导级(RF stage)偏置为AB类(VGS 略高于阈值电压)、LO 开关级偏置为饱和区,在保证转换增益(CG)的同时,为线性增强奠定基础,实测IP₁dB较 Class A偏置提升2.3dBm;创新将跨导级漏极电感(LD)与源极退化电感(LS)通过磁耦合(耦合系数 KC)形成负反馈,通过调节KC动态优化等效跨导,使IP₁dB在28/37/39GHz分别达11.32/11.06/9.85dBm,较传统源极退化提升3.5dBm。HLET 技术首次实现IP₁dB与IIP3的同步突破,动态范围较同类设计扩大15%,可耐受强干扰信号而不出现失真。

图2.(a)所提出的混合线性增强技术(HLET)(b)恒定输出压缩点下,不同转换增益(CG)对应的1dB压缩点变化(c)传统吉尔伯特单元混频器中,射频级与本地振荡器级不同偏置条件下的仿真结果

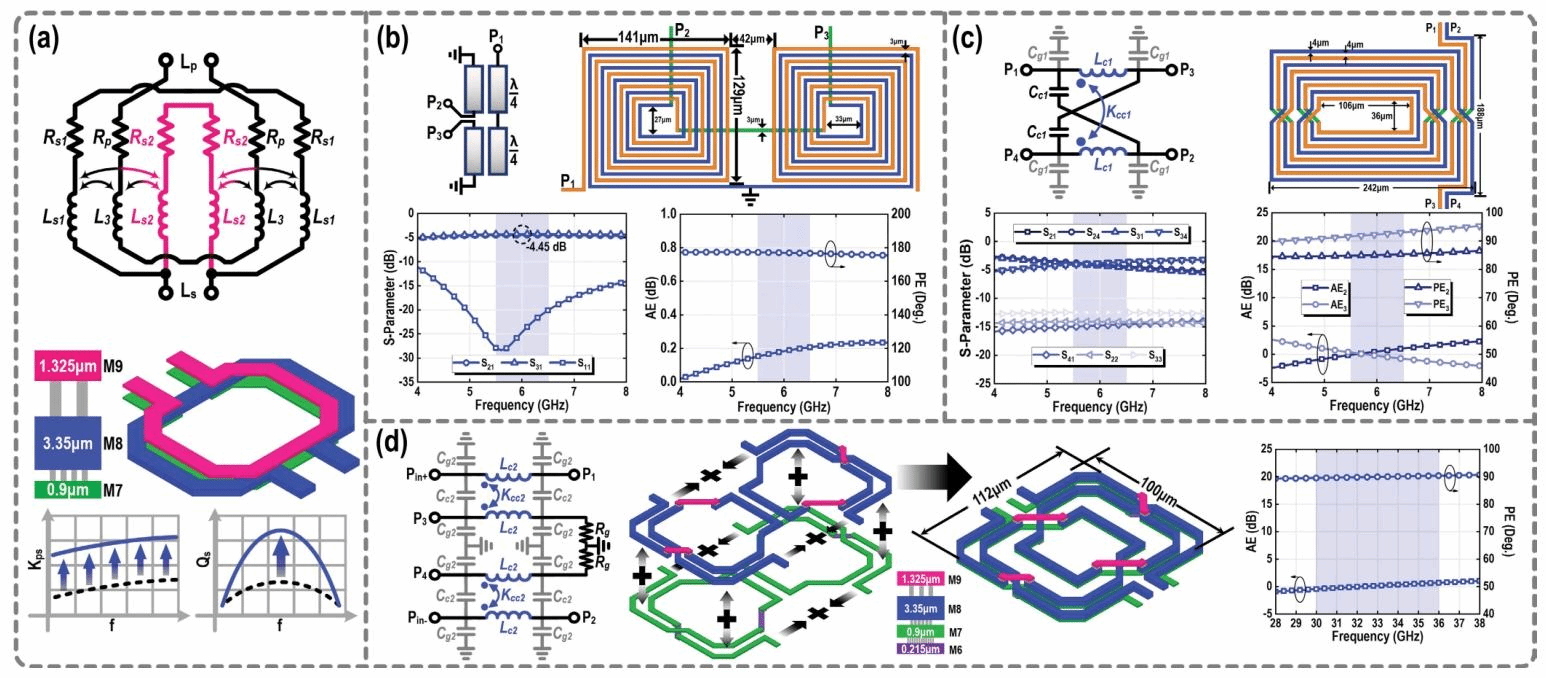

为实现双频段阻抗匹配与信号转换,团队设计系列新型无源组件,解决毫米波频段寄生效应难题。采用三层金属堆叠结构,相比传统边缘耦合变压器,耦合系数调节范围扩大40%,在24-42GHz频段内实现< -10 dB的反射系数(S₁₁),且底部绕组品质因数(Qs)提升25%;在IF频段采用单层厚金属螺旋结构,核心面积仅324×138μm²,幅度不平衡< 0.18dB、相位不平衡< 2.96°,实现差分-单端信号高效转换。

图3.(a)三明治耦合变压器的集总模型电路与电磁模型(b)所提螺旋边缘耦合Marchand巴伦的等效模型、电磁模型及其仿真结果(c)所提变压器耦合器的集总模型电路、电磁模型及其仿真结果(d)所提变压器正交网络的集总模型电路、电磁模型及其仿真结果

基于55nm体硅CMOS工艺流片的原型芯片,实测性能达到国际领先水平:24-30GHz与36-42GHz双频段内,IP₁dB达9.85-11.32dBm,IIP3达20.8-23.6dBm,同时实现高线性度与宽动态范围,在同类CMOS变频器中排名第一;LO-RF隔离> 32.7dBc、LO-IF隔离> 58.6dBc,有效避免LO泄漏;边带抑制比达27.2dB,支持额外外部滤波进一步提升抗干扰能力;1.2V供电下功耗仅26mW,较同类双频段设计降低30%;芯片总面积1.47mm²(含焊盘),较并行通道架构缩小25%;在28/38GHz频段下,64 QAM调制信号的均方根误差向量幅度分别为1.07%/1.42%,支持3 Gb/s高速数据传输,满足5G NR 要求。

本文的研究工作受到国家重点研发计划的资助,资助编号为2018YFB2202500.

文章索引:10.1109/JSSC.2024.3399125