在 5G 通信与物联网技术飞速发展的当下,低功耗、高抗干扰能力的可重构接收机成为各类新兴应用的关键核心器件。近日,天津大学微电子学院王科平教授团队在国际顶级期刊《IEEE Journal of Solid-State Circuits》发表题为 “A Low-Power Blocker-Tolerant Wideband Receiver With Bias-Tunable Mixer and Effective Switch Resistance Compensation” 的研究论文,提出一种新型低功耗抗干扰宽频带接收机设计方案,有效解决了传统接收机在高频段性能退化与功耗过高的核心矛盾。

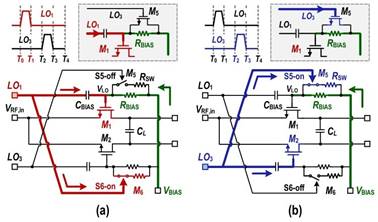

团队首次深入分析了非理想1/N LO占空比(N=4)与有效开关电阻对混频器优先接收机的影响。研究发现,高频下LO时钟上升/下降时间占周期比例增大,导致有效导通占空比从理想25%降至18%(2.4GHz时),使得有效开关电阻显著增大,引发噪声系数恶化3dB、带外三阶截点下降7.1dB。为此,团队提出动态偏置可调混频器方案:通过数字基带自动生成随频率线性变化的偏置电压,在高频段增大偏置电压以降低开关电阻,抵消占空比退化的影响。蒙特卡洛仿真验证显示,该技术可将高频段有效开关电阻波动控制在1Ω以内,噪声系数改善1.1dB,带外三阶截点提升4.5dB。

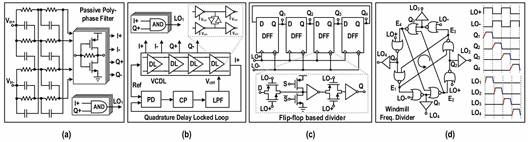

图1.(a) 无源多相滤波器、(b) 正交延迟锁定环、(c) 基于触发器的分频器和 (d) 风车分频器的示意图

传统RC耦合偏置方案存在电荷累积导致的稳态电压跌落与长建立时间,且高偏置电压易引发MOS管栅氧击穿风险。团队创新设计辅助开关电荷补偿电路:利用差分路径 LO 脉冲控制辅助开关,将建立时间缩短至50ns以下;通过优化NOR门中PMOS/NMOS尺寸比,避免时钟重叠;同时将混频器栅源电压钳位在安全范围,兼顾性能与器件可靠性。

图2.所提出的带电荷补偿的偏置可调混频器在不同时刻的详细电路及原理

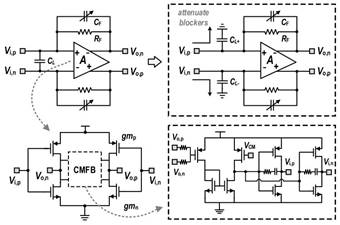

为在低功耗下实现高抗干扰能力,团队构建“射频辅助滤波 + 基带高阶滤波”的双重抑制架构:射频端引入辅助N路径底板滤波器,与主滤波路径形成等效RLC谐振网络,将选择性参数β从50/12提升至50/8.5,LO驱动功耗降低30%;基带端采用模拟有限冲激响应(AFIR)滤波器,相比传统Gm-C滤波器,在32/80MHz时钟下实现4/10MHz可调带宽,滤波斜率达38dB/10MHz,30MHz偏移处干扰抑制比达53dB。

图3.带共模反馈(CM-FB)的跨阻放大器(TIA)详细电路图

基于55nmCMOS 工艺流片的接收机原型,在0.4-2.6GHz 宽频带范围内展现出优异性能:双边带噪声系数(DSB-NF)仅2.4-3.5dB;10/80MHz偏移处带外三阶截点(OB-IIP3)达+15.4/+19.2dBm,远超同类设计;总功耗仅5.4-11.8mW,LO 驱动功耗低至2.9mW/GHz,较现有混频器优先架构降低3-10倍。

该研究得到国家自然科学基金项目(62371332)支持。

文章索引:10.1109/JSSC.2025.3529681